Page 113 - 2024-Vol20-Issue2

P. 113

109 | Maddu & Bhasme

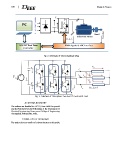

Fig. 2. Schematic of Wavect hardware setup

Fig. 3. Schematic of Three-phase, Two-level VSI with an RL load

ACKNOWLEDGMENT

The authors are thankful to AICTE, New Delhi for provid-

ing the National Doctoral Fellowship at the Department of

Electrical Engineering, Government College of Engineering,

Aurangabad, Maharashtra, India.

CONFLICT OF INTEREST

The authors have no conflict of relevant interest to this article.