• •

1 1

\_\_\_\_\_

# algorithm for 2D-data array addition using digit-decomposition-plane representation

Sabah S. Alsheraidah

Basrah Technical Institute

Department of Computers

System Basrah-Iraq

E-mail: sabahhd@yahoo.com

Alaa A. W. Al-Saffar Basrah Technical Institute Department of Electronics Basrah-Iraq.

Mohmmed A. A. Al-Ebbady Basrah University College of Engineering Department of Computers. Abstract. In this paper, optical scalable parallel and high-speed 2D data array adder for trinary signed-digit (TSD) number is proposed. The digit-decomposition-plane (DDP) coding method is used to represent the 2D TSD data arrays. The algorithm performs parallel TSD addition in constant time independent of the size of the TSD data arrays. The design describes methodology to involve two-step TSD adder. The TSD addition is expressed with several combination logic formulas that are newly derived. Optical implementation with classical optical elements is suggested for proposed TSD adder. Preliminary demonstration example is also described.

### 1- Introduction

Today, the world is in need to ultrahigh speed processing devices, to fulfill the theories of the new technologies that require very high speed. The electronic digital processing devices are developed to match these demands but they stay limited because the parallelism and high-speed of the digital systems are complex in implementation.

The new technology uses the light in large parts of the processing systems, and called "

Optical Computing Systems" [1, 2].

The optical processing systems had been leaded to many advantages, which might needed for very high speed processing systems. The important advantage was the parallelism. The parallelism of optical processing systems was flexible and not complex in implementation, so data in one-dimension and multi-dimension can be processed [3].

In optical processing systems, the light signals can pass through each other without 12 interacting or influencing the data carried by.

This feature overcame the problem that named "Von Neuman bottleneck" in the digital computers. It gave a large communication links between processing units in a small area.

These optical techniques had been established using many parallel algorithms in order to perform the arithmetic operations. Some of these parallel algorithms used the redundant binary numbers [4]. The other used a multi-leveled number system based on residue arithmetic algorithm. Also, parallel optical logic gates had been suggested to process large amounts of data in parallel and in speed of light [5]. Carry-free full parallel optical one-step TSD adder using symbolic substitution (SS) technique is studied in [6]. Also, a receded TSD adder using SS technique had been presented in [7].

Recently, optical parallel scalable three-step modified signed-digit (MSD) adder for large-scale two 2D MSD data arrays coded by DDP representation had been studied [8]. Also, high speed parallel optical adder for QSD number using digit-decomposition-plane (DDP) representation is suggested in [9].

In this research, we propose a parallel digital addition algorithm to array calculation. The algorithm for addition of two n-digit  $M \times N$  TSD data arrays will generate  $M \times N \times (n+1)$  partial terms, where M is the number of rows and N is the number of columns, while n is the number of TSD digit per one number. The proposed techniques

perform parallel TSD addition in constant time, and are of great benefit to array calculation. The digit-decomposition-plane (DDP) coding method is used to represent the 2D TSD data arrays. DDP is used in this work because there are two apparent features of this coding method. The first one is that any DDP plane is the complement of the superimposing plane of the other planes. The superimposing plane is obtained by accumulated the bright and dark pixels in one plane. The second one is that if all DDP planes are superimposed, the result will be a totally transparent plane. The design describes methodology for obtaining two-step TSD adder. The TSD addition has been described with several combination logic formulas and then implemented using simple optical elements, such as beam splitters, mirrors, beam combiners, light sources array, and light detectors array. Various examples are performed in order to test computer simulation.

#### 2 - TSD two-step adder

The two-step adder for TSD numbers is expressed according to the following two equations:

**Step 1:**

$$x_i + y_i = 3c_i + s_i$$

(1)

**Step 2:**

$$S_i + C_{i-1} = Z_i$$

(2)

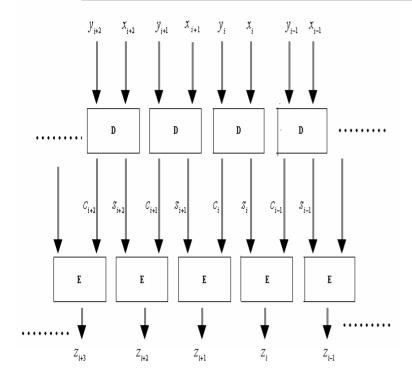

Figure. 1 presents the block diagram of this adder. Boxes D (first step) add the CP digits  $(x_i, y_i)$  of addend number X and

**Fig. 1:** Block diagram of two-step TSD adder, where the functional blocks D and E employ the TSD addition rules shown in Eqs. (1) and (2), respectively.

augend's number Y, which are both ndigit TSD numbers, produce to the  $(s_i,c_i)$ intermediate sum and carry according to the computational rules of Table 1-a. Boxes E (second step) add  $S_i$  to  $C_{i-1}$ , to obtain the final result  $Z_i$  depending on computational rules of Table 1-b. First. the combinations 25  $CP(X_i, y_i)$  can be classified into 9 groups  $(G_1 - G_0)$  [6]. Each group  $G_i$  represents one computational rule of the first step addition. Table 1-a considers these 9 rules in order to obtain S<sub>i</sub> and C<sub>i</sub> according to the values of

Table 1: Truth tables for TSD arithmetic

| groups     | current pair CP                             | intermediate results |   |

|------------|---------------------------------------------|----------------------|---|

| G,         | $(x_i, y_i)$                                | 5                    | с |

| G,         | (2,2)                                       | 1                    | 1 |

| $G_{2}$    | (2,1),(1,2)                                 | 0                    | 1 |

| $G_{_3}$   | (2,0),(0,2),(1,1)                           | ī                    | 1 |

| G,         | (2,1),(1,0),(0,1),(1,2)                     | 1                    | 0 |

| $G_s$      | (2, 2), (2, 2), (1, 1), (1, 1), (0, 0)      | 0                    | 0 |

| $G_{_{6}}$ | (2,1),(1,0),(0,1),(1,2)                     | ī                    | 0 |

| G,         | $(\bar{2},0),(0,\bar{2}),(\bar{1},\bar{1})$ | 1                    | ī |

| G,         | $(\bar{2},\bar{1}),(\bar{1},\bar{2})$       | 0                    | ī |

| G,         | (2,2)                                       | Ī                    | Ī |

(a)

| groups      | intermediate results                  | final results           |

|-------------|---------------------------------------|-------------------------|

| $H_{_{i}}$  | (s,,c_i)                              | $\boldsymbol{z}_{_{i}}$ |

| $H_{\perp}$ | (1,1)                                 | 2                       |

| $H_z$       | (1,0),(0,1)                           | 1                       |

| $H_{3}$     | (1,1),(1,1),(0,0)                     | 0                       |

| $H_{_{+}}$  | (1,0),(0,1)                           | Ĩ                       |

| $H_s$       | $(\bar{\mathbf{l}},\bar{\mathbf{l}})$ | 2                       |

**(b)**

the two digits of the i-th CP. Also, In Table 1-a, it is clear that each  $s_i$  and  $\mathbf{C}_i$  has only three TSD weights  $\{1,0,\bar{1}\}$ , so there are 9 combinations of  $(\mathbf{S}_i,\mathbf{C}_{i-1})$  can be classified into 5 groups  $(H_1-H_5)$  as shown in Table 1-b to represent the computational rules of the second step addition. So, the final result will be (n+1)-digit TSD number.

## 3- TSD addition with DDP representation

DDP representation had been proposed by *Hongxin Huang* and *et.al* [8]. It is an extension for bit-plane representation method.

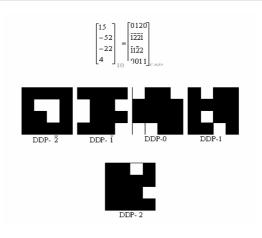

DDP representation can be applied to code large 2D data arrays of TSD numbers. The 2D TSD numbers data array can be coded using DDP representation in 5 DDP planes (DDP- 2, 1,  $0,\bar{1},\bar{2}$ ). Figure 2 shows example for TSD data array coded by DDP scheme. The addend A and augend's B M×N×n TSD arrays will be decomposed into 5 DDP planes for each one, they are  $(A2,A1,A0,A\bar{1},A\bar{2})$  and  $B2,B1,B0,B\bar{1},B\bar{2})$ .

Two steps are used to derive the logical formulas in order to implement TSD adder.

## • First-step:

In Table 1-a, the intermediate sum S<sub>i</sub> will be 1 if the following rule is succeeded:

$$IF(\mathbf{x}_{\dot{1}}, y_{\dot{i}}) = (2,2)OR(2,\bar{1})OR(1,0)OR(0,1)OR(\bar{1},2)$$

$OR(\bar{2},0)OR(0,\bar{2})OR(\bar{1},\bar{1})THEN\mathbf{s}_{\dot{1}} = 1$  (3)

$x_i$  and  $y_i$  equal to 2,1,0, $\bar{1}$ , and  $\bar{2}$  digits are separated and decomposed to the (j,i)-th pixels of A and B DDP planes. Then, equation (3) can be rewritten as:

$$s1_{ji} = a2_{ji} *b2_{ji} + a2_{ji} *b\bar{1}_{ji} + a1_{ji} *b0_{ji}$$

$$+ a0_{ji} *b1_{ji} + a\bar{1}_{ji} *b2_{ji} + a\bar{2}_{ji} *b0_{ji}$$

$$+ a0_{ji} *b\bar{2}_{ji} + a\bar{1}_{ji} *b\bar{1}_{ji}$$

$$(4)$$

The plane S1 (DDP-1 plane) of the intermediate sum array S can be obtained in parallel depending on the following rule:

Fig. 2: Optical DDP coding of TSD data array

$$S1 = A2 * B2 + A2 * B\overline{1} + A1 * B0 +$$

$$A0 * B1 + A\overline{1} * B2 + A\overline{2} * B0$$

$$+ A0 * B\overline{2} + A\overline{1} * B\overline{1}$$

(5)

This can be simplified to:

$$S1 = (A2 + A\bar{1}) * (B2 + B\bar{1}) + A0 * (B1 + B\bar{2}) + (A1 + A\bar{2}) * B0$$

(6)

The intermediate sums and carries of all adding numbers included in A and B arrays will be generated in parallel in six DDP planes (S1, S0, S $\bar{1}$  and C1, C0, C $\bar{1}$ ). In the same way of obtaining S1 plane, the rest five DDP planes can be also obtained from Table 1-a.

$$S\bar{l} = (A1 + A\bar{2})*(B1 + B\bar{2}) + A0*(B2 + B\bar{l})$$

+  $(A2 + A\bar{l})*B0$  (7)

$$S0 = (A2 + A\bar{1})*(B1 + B\bar{2}) + (A1 + A\bar{2})*(B2 + B\bar{1}) + A0*B0$$

(8)

$$C1 = (A2 + A1)*(B2 + B1)$$

+  $A2*B0 + A0*B2$  (9)

$$C\bar{1} = (A\bar{1} + A\bar{2}) * (B\bar{1} + B\bar{2})$$

+  $A\bar{2} * B0 + A0 * B\bar{2}$  (10)

$$C0 = (A2 + A1)*(B\overline{1} + B\overline{2}) + (A\overline{1} + A\overline{2})*(B2 + B1) + A0*(B1 + B\overline{1})(A1 + A0 + A\overline{1})*B0$$

(11)

# • Second-step:

Table 1-b shows the computational rules of the second-step in two-step TSD adder. Simply, the logical formulas of the second-step can be derived from the S1, S0, S $\bar{1}$ , C1, C0, and C $\bar{1}$  planes which are generated in the first-step. The first rule in the Table 1-b is:

$$IF(s_i, c_{i-1}) = (1,1) \text{ THEN } z_i = 1$$

(12)

Similar from the first-step phase, we can get the five TSD DDP planes of the final results Z2, Z1, Z0,  $z\bar{1}$ , and  $Z\bar{2}$  according to the following rules:

$$Z2 = S1 * C'1$$

(13)

$$Z1 = S1 * C'0 + S0 * C'1$$

(14)

$$Z0 = S1 * C'\bar{1} + S0 * C' + S\bar{1} * C'1$$

(15)

$$Z\bar{1} = S\bar{1} * C'0 + S0 * C'\bar{1}$$

(16)

$$Z\overline{2} = S\overline{1} * C'\overline{1} \tag{17}$$

The  $M \times N \times n$  TSD array A is added with the  $M \times N \times n$  TSD array B in parallel and will

generate the M×N×(n+1) TSD array which is presented the final results, and indicated by planes Z2, Z1, Z0,  $\overline{Z1}$ , and  $\overline{Z2}$ .

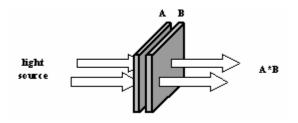

# 4- Optical implementation

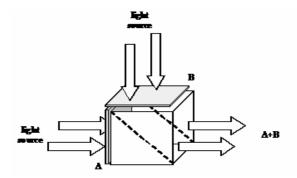

The optical hardware schemes of this parallels **TSD** adder arrav he implemented practically using simple optical tools. The logical AND and OR are the main operations in the logical formulas. The principles handled for AND and OR operations will be considered to realize our suggestion for TSD adder [5, 8]. Logical AND can be achieved optically by cascading two DDP planes, each of one array, with same dimensions and pixel resolutions. The light beams will be applied on each pixel of the first plane. These beams will pass through the transparent pixel (1) and blocked by opaque pixel (0). Thereby, four combinations of transparent (1) and opaque (0) pixels of the two DDP planes will be presented:  $(1 \times 1)$ ,  $(1\times0)$ ,  $(0\times1)$ , and  $(0\times0)$ . Only in case  $(1\times1)$ the light beam will pass through the two cascaded planes. So, this optical AND can process M×N×n binary AND operations in Fig. 3 parallel. shows the optical implementation of the logical AND. a pixelwise addition in parallel for the corresponding Optical logical OR can be realized using beam combiner (BC). BC performs light beams of the two packages passed through two DDP planes and fallen onto the two BC input surfaces. Three pixel-wise addition cases will be gain: (1+0), (0+1), and (0+0).

Fig. 3: AND gate optical implementation

Fig. 4: OR gate optical implementation

The case (1+1) will never appear because the pixel-wise addition is done between two DDP planes of the same array. So,  $M \times N \times n$  binary OR operations will be done in parallel. Fig. 4 illustrates the optical implementation of the logical OR.

The proposed parallel optical two-step TSD adder operation can be explained as following:

- 1- The input  $M \times N \times n$  DDP-planes of the first step will be illuminated by Laser sources to enter the optical system for processing.

- 2- Light detector arrays (LDAs) in the end of optical scheme of the first step will detect the DDP-planes of the intermediate results that produced by the first step.

- 3- These optical signals will be converted to electrical signals and passed to the optical implementation of the second step.

4- The input DDP-planes of the second step will be addressed in parallel by these electrical signals to form the sufficient expanded and shifted copies of the intermediate results. Expanding and shifting means that, one pixel is necessary to be padded to the LSB and MSB pixel position of the detected DDP-planes of the intermediate carry and intermediate sum, respectively.

5- Finally, the LDAs will detect the optical signals that represent the DDP-planes in the final result array, which will be  $M \times N \times (n+1)$  TSD array.

The above points will present the complete optical implementation of the suggested parallel optical two-step TSD adder with the consideration of the following explanations:

BC : denotes a beam combiner.

BS: denotes a beam splitter.

: denotes a mirror.

: denotes SLM (DDP plane), LDA, or CMP.

: the direction of the light signal emitted by an optical source.

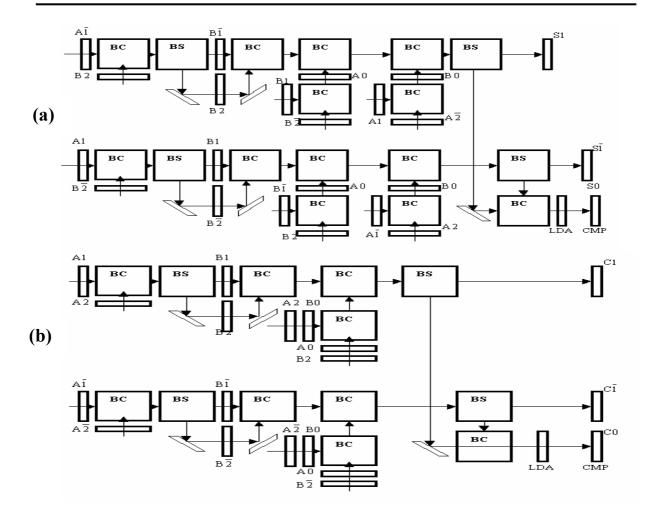

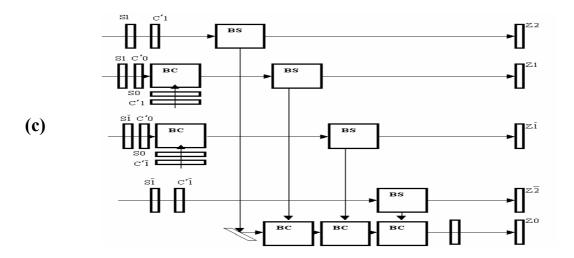

The optical implementation of the two steps 2D TSD array is shown in Fig. 5.

Fig. 5: Optical implementation of the 2D –data array TSD adder

- (a): First-step, (intermediate sum generation).

- **(b):** First-step, (intermediate carry generation).

- (c): Second-step, (final results generation).

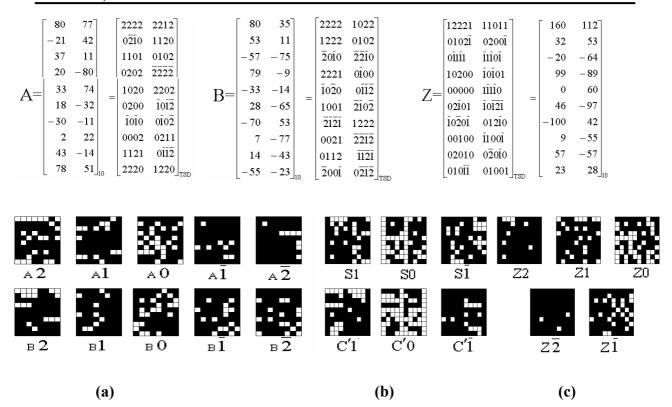

Fig. 6: Simulation results of the two-step 2D-data array TSD adder.

- (a) A and B SLM inputs.

- (b) First-step intermediate Sum and Carry generations.

- (c) Second-step (final results generations).

### 5- Simulation results

The computer program using C++ language is used to simulate the optical implementation of the proposed TSD adder. This program is built and executed for two-step TSD adder using DDP representation. The two 10×2×4 TSD arrays A and B will be used to test the operation of the proposed TSD array adder. Figure 6 shows the DDP-planes of the two TSD arrays A and B. The First-step intermediate Sum and intermediate Carry generations are presented in Fig. 6-b. While the final results are shown in Fig. 6-c.

## 6- Conclusions

In this work, the parallel scalable optical two-step TSD adder is proposed. The M×N×n TSD data arrays are processed using the apparent features of the DDP coding method. Computer programming is used to simulate the logical formulas of the TSD adder. Practical example is discussed and verified by computer simulations. It is found that the simulation results are confidence, and that the newly technique is performed correctly. Simple classical optical tools are suggested successfully to implement this TSD adder. Tools like AND gate, OR gate, BS,

BC, LDA, CMP, SLM, and mirrors are used to constructed TSD adder.

## **References**

- [1] T. Stouraitis and C. Chen," Hybrid Signed-Digit Logarithmic Number System Processor," *Proc.IEEE.*, Vol. 140, No. 11, pp. 205-210, 1993.

- [2] N. Savage," SLMs Enter Fields from Photolithography to Optical Computing," *Oemagazine.com/from*the magazine/mar03/prodtrends.

html\, 2003.

- [3] P. A. Mitkas and L. J. Irakliotis," Three-Dimensional Optical Storage for Data Base Processing," *Opt. Memories Neural Net.*, Vol. 3, 1994.

- [4] S. Zhang and M. A. Karim," Optical Arithmetic Processing Using Improved Redundant Binary Algorithm," *Opt.Eng.*, Vol. 38, No. 3, pp. 415-421, March 1999.

- [5] S. Kawai, Y. Tashiro, H. Ichinose, and K. Kasahara," Cascade-Connective Optical Parallel Logic Processor Using Electrophotonic

- Devices," *Appl.Opt.*, Vol. 31, No.2, pp.178-185, Jan. 1992.

- [6] A. K. Cherri," Signed-Digit Arithmetic for Optical Computing: Digit Groping and Pixel Assignment for Spatial Coding," *Opt.Eng.*, Vol. 38, No. 3, pp. 422-431, March 1999.

- [7] M. S. Alam," Parallel Optoelectronic Trinary Signed-Digit Division," *Opt.Eng.*, Vol. 38, No. 3, pp. 441-448, March 1999.

- [8] H. Huang, M. Itoh, and T. Yatagai,

"Optical Scalable Parallel

Modified Signed-Digit Algorithms

for Large Scale Array Addition and

Multiplication Using DigitDecomposition-Plane

Representation," Opt.Eng., Vol .38,

No. 3, pp. 432-440, March 1999.

- [9] A. Al-Saffar, S. Alsheraidah, and Al-Ebbady," High Speed Parallel Optical Adder for QSD Number Using Digit-Decomposition-Plane Representation," Accepted in the Journal of Basrah Researches, College of Education, Basrah University, April 2006.